Upgrade

A Single-Chip Wideband

Digital Receiver for the

Australia Telescope

Compact Array

John Tuthill | 19 August 2025

Nation as the Traditional Owners of the land and coastal waters of this place I'm presenting from today. I pay my respect to their Elders past and present and extend this to any First Nations people here today.

#### The team:

Mia Baquiran, Daniel George, Samantha Gordon, Paul Roberts, Grant Perry, Chris Phillips, Peter Roush

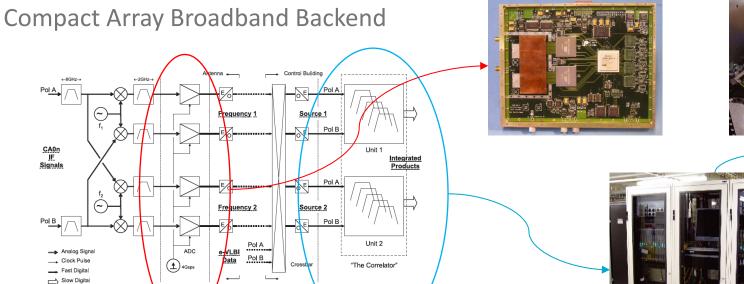

# BIGCAT Project: Broadband Integrated GPU Correlator for ATCA Telescope

IF Conversion

System per Antenna

Digitisation

Data Transport &

Switching

CABB Digitisers: 4,096 MSamp/sec, 10-bit custom-designed interleaved converters CABB FPGA Channeliser and Correlator card: Xilinx Series-4 FPGAs (Virtex-4 discontinued 2015)

Images: W. E. Wilson, et. al., The Australia Telescope Compact Array Broad-band Backend: description and first ABB FPGA Correlator cabinet results, Monthly Notices of the Royal Astronomical Society, Volume 416, Issue 2, September 2011, Pages 832–856, https://doi.org/10.1111/j.1365-2966.2011.19054.x

Digital Signal

Processing

Combined Antennas

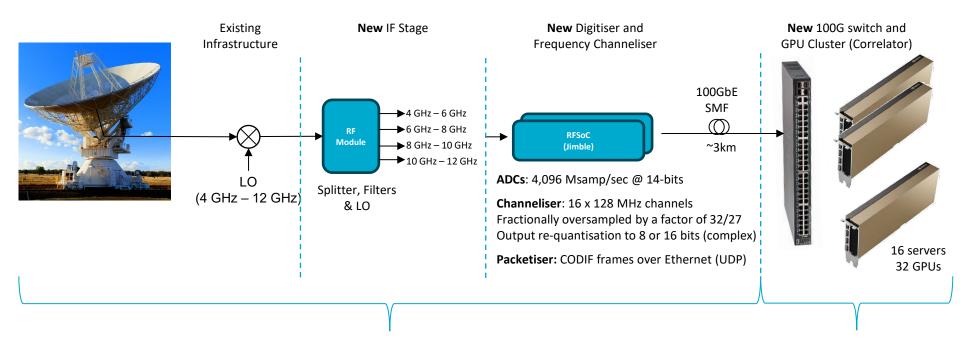

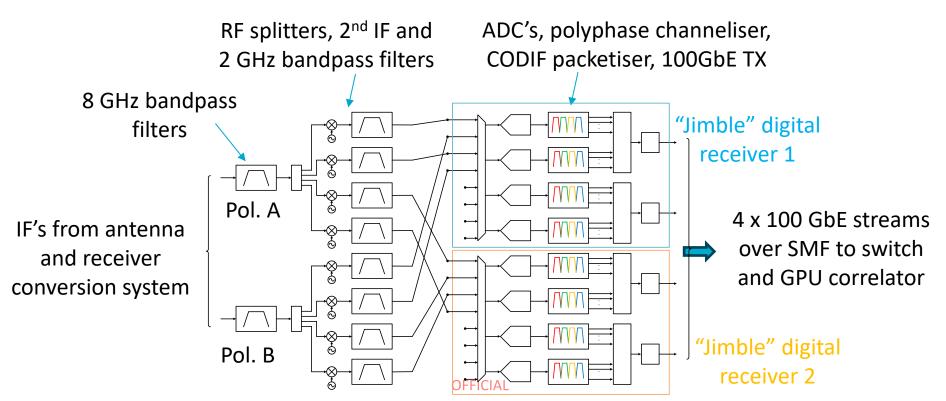

## BIGCAT Digital Systems Upgrade

Per Antenna

**Correlator Room**

## BIGCAT System Overview per Antenna

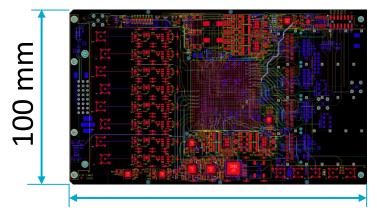

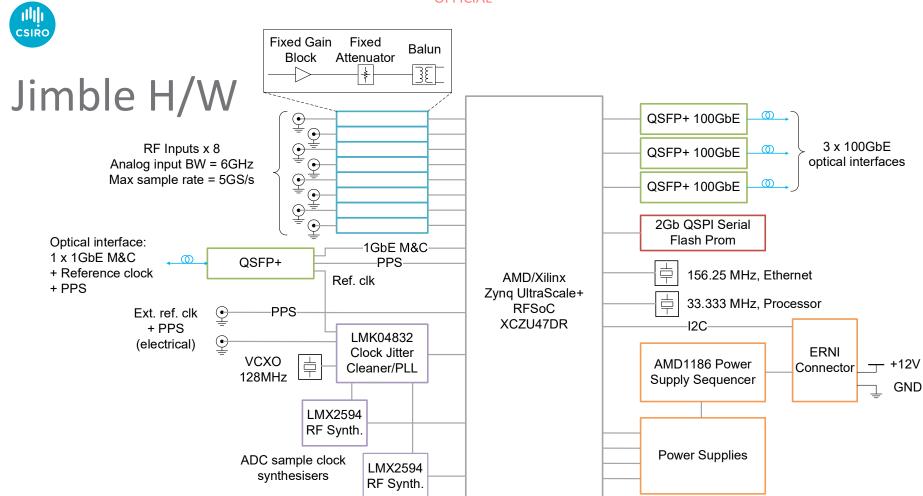

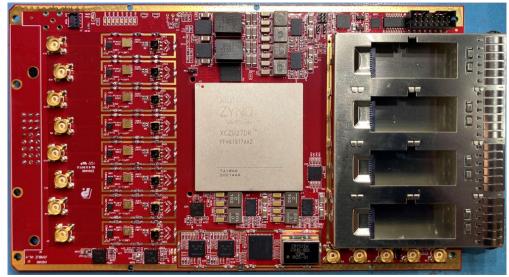

## "Jimble" Digital Receiver Hardware

- Analogue BW = 6 GHz (processed BW = 2 GHz)

- 8 x RF inputs, simultaneous sampling @ 4096 MHz and 14-bits

- 2 x 100GbE QSFP+ outputs for BIGCAT (3 available)

- Eurocard form factor @ ~70W per card

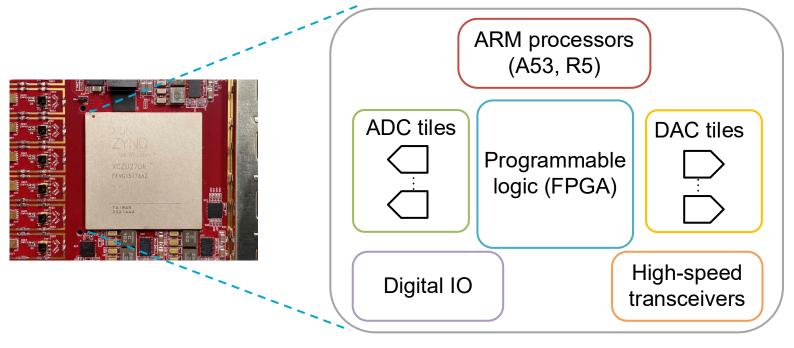

## AMD/Xilinx Zynq UltraScale+ RFSoC

**OFFICIAL**

**OFFICIAL**

## Sample clock VCXO selection

- Sample clock jitter couples directly to output sample noise

- Mechanical vibration (microphonic) effects on VCXO must also be considered

| Measurement Integration range is 100Hz to 1MHz |           |                     |                     |           |

|------------------------------------------------|-----------|---------------------|---------------------|-----------|

|                                                | Frequency | Int. Phase          |                     |           |

| Model                                          | (MHz)     | Noise (dBc)         | rms jitter          | radians   |

| Crystek                                        | 128       | <mark>-79.23</mark> | <mark>192 fs</mark> | 154 uRad  |

| Crystek+Vibrations                             | 128       | <mark>-65.74</mark> | <mark>907 fs</mark> | 730uRad   |

|                                                |           |                     |                     |           |

| ABLNO_V_125                                    | 125       | -77.65              | 236 fs              | 185 uRad  |

| ABLNO_V_125+Vibrations                         | 125       | -68.84              | 651 fs              | 511 uRad  |

|                                                |           |                     |                     |           |

| Rakon V4180                                    | 122.88    | -83.86              | 117 fs              | 91 uRad   |

| Rakon V4180 + Vibrations                       | 122.88    | -60.87              | 1.66 ps             | 1.28 mRad |

## Reference Clock and Timing Synchronisation

## The heart of a multi-channel synchronous sampling receiver 3-step process:

- 1. Hardware synchronisation of the board clock across multiple Jimble boards

- ADC sample clocks always phase locked and edge-aligned

- SYSREF signals synchronised using the distributed PPS

- 2. ADC synchronisation

- Multi-tile sync process across the RFSoC devices using the SYSREF signal and a target latency

- 3. DSP and streaming output synchronisation and time-stamping

- PPS synchronised event signal

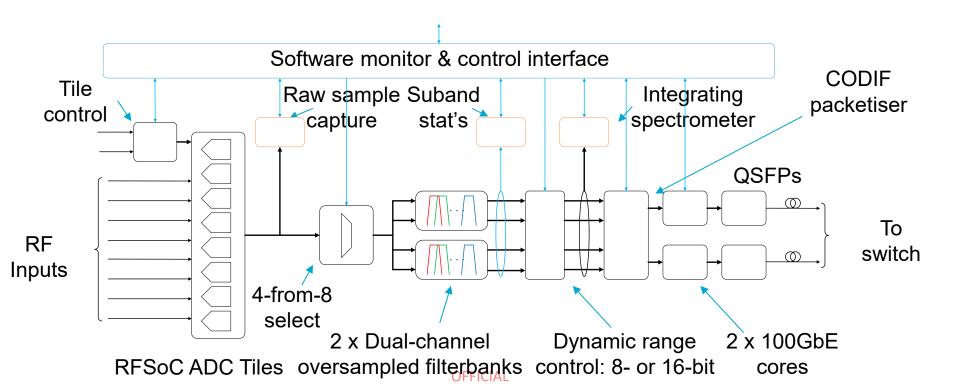

## FPGA Firmware and Signal Path

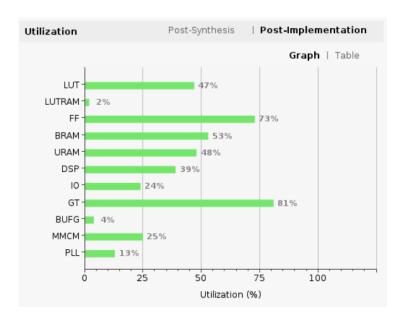

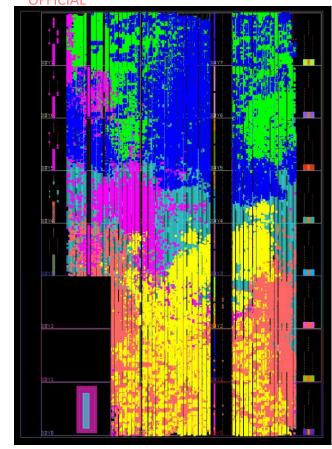

## **FPGA Build**

FPGA resource utilisation

FPGA floorplan

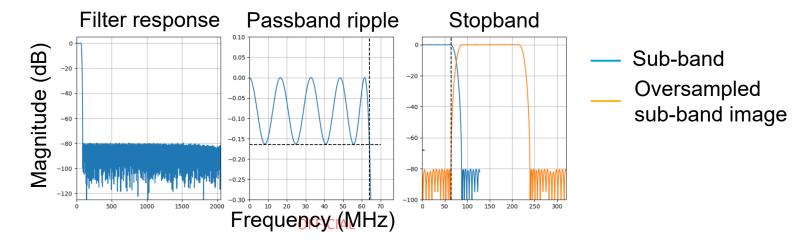

## Polyphase Filterbank Frequency Channeliser

- Prototype filter: 576 taps

- Oversampling ratio = 32/27

- Stop-band attenuation > 80dB

- Pass-band ripple <0.2dB</li>

## Streaming Data Interface

- 2 x 100GE (3 x 100GE interfaces possible)

- CODIF encapsulation in Ethernet UDP

- CODIF: <u>CSIRO Oversampled Data Interchange Format</u>

- Originally an extension of the VDIF standard to support fractionally oversampled data streams

- 8 x 64-bit word header: timing, source and data payload details

- Data array payload: user-defined length typically constrained by network factors such as MTU size.

## Software Monitoring and Control

- Python and Rust framework using the open source ZeroMQ messaging lib.

- Controls:

- initialisation and synchronisation process

- Dynamic range in the streaming output

- Configuration, starting and stopping of the 100GE streams

- Precisely timed event-based system functions

- Monitors:

- Jimble hardware status power supplies, temperatures, reference oscillator status

- Signal chain ADC histograms, subband statistics, integrated power spectra

- Output stream status

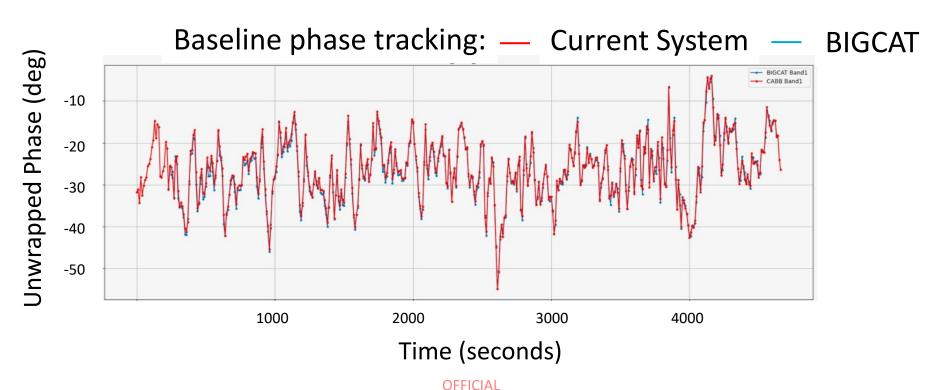

## Performance against existing system

## Results

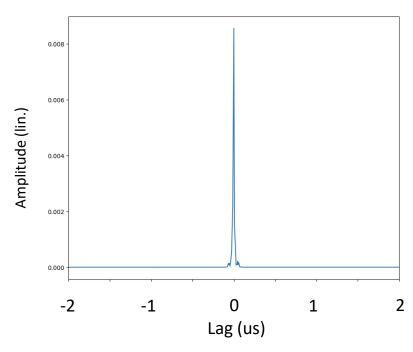

Two-Jimble cross-correlation lag spectrum

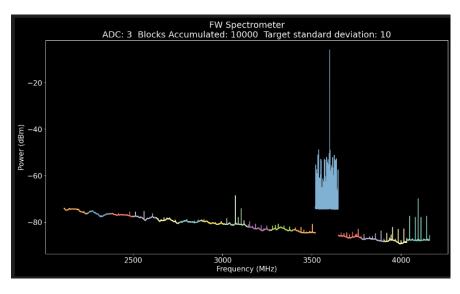

Subband integrated power spectrum from FPGA firmware spectrometer (Strong test tone evident in 12<sup>th</sup> subband)

#### Jimble digital receiver

## Thank you

#### **Space and Astronomy**

Dr John Tuthill Team Lead – Digital Signal Processing

+61 2 9372 4392 john.tuthill@csiro.au csiro.au/astronomy